Утвержден ЮФКВ.431268.019РЭ-ЛУ Удостоверен ЮФКВ.431268.019РЭ-УД Микросхема интегральная 1888ВВ018А Руководство по эксплуатации ЮФКВ.431268.019РЭ Инв.№дубл. Справ.№ Инв.№подл. Подп. и дата Взам.инв.№ Подп. и дата Kap- 20.04.2018 31918-3 31918-4

## Оглавление

| Вв          | едени          | 1е      | ••••••        | •••••         | •••••                        | ••••••                     | •••••                         | ••••• | ••••••    | 3       |

|-------------|----------------|---------|---------------|---------------|------------------------------|----------------------------|-------------------------------|-------|-----------|---------|

| 1           | Опи            | сание   | и работа      | а СБИ         | IC 1888BB                    | 018A                       | •••••                         | ••••• |           | 4       |

| 1           | .1             | Назначе | ение СБ       | ИС 18         | 88BB018A                     |                            |                               |       |           | 4       |

| 1           | .2             | Основн  | ые хараі      | ктерис        | стики СБИО                   | C 1888BB018A               |                               |       |           | 5       |

| 1           |                |         |               |               |                              | BB018A                     |                               |       |           |         |

| 1           |                |         | -             |               |                              | 018A                       |                               |       |           |         |

|             |                |         |               |               |                              | BB018A                     |                               |       |           |         |

| •           | 1.5.1          | -       | -             |               |                              | іх сигналов                |                               |       |           |         |

|             | 1.5.2          |         |               |               |                              | терфейса РСІ               |                               |       |           |         |

|             | 1.5.3          |         | _             |               |                              | интерфейса РС              | _                             |       |           |         |

|             | 1.5.4<br>1.5.5 |         | -             |               | •                            | их резисторов контроллером |                               |       |           |         |

|             | 1.5.6          |         | -             | _             |                              | контроллеров<br>G          |                               | , .   | `         |         |

| 2           |                |         |               |               |                              | онструктивн                |                               |       |           |         |

| _           |                | -       |               |               |                              |                            |                               |       |           | 35      |

| 2           | 2.1            | Состав  | и распол      | тожен         | ие внешних                   | к выводов СБИ              | IC 1888BB01                   | 8A    |           | 35      |

|             |                |         | _             |               |                              | и СБИС 1888В               |                               |       |           |         |

|             |                | - '     |               | -             | -                            |                            |                               |       |           |         |

|             |                |         |               |               |                              | СБИС 1888ВВ                |                               |       |           |         |

| 2           |                |         |               |               |                              | IC 1888BB018               |                               |       |           |         |

| 3           | При            | менені  | ие СБИ        | C <b>1888</b> | 8BB018A                      | •••••                      | •••••                         | ••••• | ••••••    | 48      |

| 3           | 3.1            |         |               |               |                              | ия СБИС 1888               |                               |       |           |         |

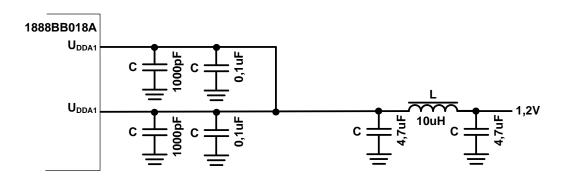

|             | 3.1.1          |         |               |               |                              | на входах пита             |                               |       |           |         |

|             | 3.1.2          |         |               |               |                              | нию функцион               |                               |       |           |         |

| 3           | 3.2            | Внутре  | ннее сам      | отест         | ирование С                   | СБИС 1888ВВО               | 018A                          |       |           | 51      |

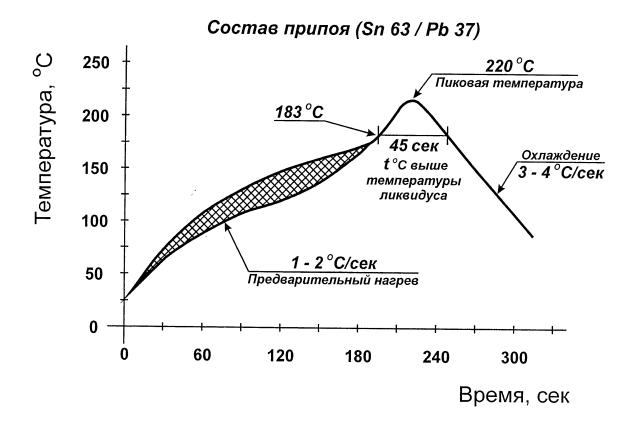

| 3           | 3.3            | Режимь  | ы пайки       | СБИС          | 1888BB01                     | 8A                         |                               |       |           | 53      |

| 4           | Xpa            | нение ( | СБИС 1        | 888BI         | B018A                        | •••••                      | •••••                         | ••••• | ••••••    | 54      |

| 5           | Tpa            | нспорт  | ировані       | ие СБ         | ИС 1888ВІ                    | B018A                      | •••••                         | ••••• |           | 55      |

| 6           | -              | -       | -             |               |                              | •••••                      |                               |       |           | 56      |

| Ū           | JIH            | лиэаци  |               | 2 1000        | , <b>DD</b> 0 1 0 1 <b>1</b> |                            | •                             |       |           |         |

|             |                |         |               |               |                              |                            |                               |       |           |         |

|             |                |         | Γ             |               |                              |                            |                               |       |           |         |

|             |                |         |               |               | <u> </u><br> -               | Ю                          | ФКВ.431268.01                 | OP3   |           |         |

| Іист        | N∘ д           | цокум.  | Подп.         | Дата          | -                            | 10                         | ΨND.401200.01                 | 01 0  |           |         |

| аб.         | Ше             | пухин   |               |               |                              |                            |                               | Лит.  | Лист      | Листов  |

| В.          |                | руков   |               |               | Микросхема интегральная А 2  |                            |                               |       | 57        |         |

| тд.         |                | ников   |               |               | _                            | 1888BB018A                 |                               |       |           |         |

| ITP.<br>3.  | Вих            | крова   |               |               | Duron                        | одство по экспл            | IVataluuu                     |       |           |         |

| s.<br>N⊵ по | L<br>одл.      | Полг    | <br>ı. и дата | I<br>Ba       | гуков<br>зам. инв. №         | Инв. № подл.               | <u>гуатации</u><br>Подп. и да | та Т  | Перв. при | именен. |

| 918-        |                |         | 20.04.20      |               | 31918-3                      |                            |                               | -     | ЮФКВ.43   |         |

|             |                | people- |               |               |                              |                            |                               |       |           |         |

Оглавление .......2

## Введение

Микросхема интегральная 1888ВВ018А (далее по тексту СБИС 1888ВВ018А) предназначена для организации обмена информацией по интерфейсу PCI Express и представляет собой одноканальный приемопередатчик шины PCI Express физического уровня.

В данном руководстве по эксплуатации представлено описание общей структуры и функционирования СБИС 1888ВВ018А, отражены особенности применения СБИС и приведены ее электрические и конструктивные параметры.

|      |         |          |                 |      |            |                   |              | Лист |  |  |  |

|------|---------|----------|-----------------|------|------------|-------------------|--------------|------|--|--|--|

|      |         |          |                 |      |            | ЮФКВ.431268.019РЭ |              |      |  |  |  |

| Изм. | Лист    | № докум. | Подп.           | Дата |            |                   |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата        |      | Взам.инв.№ | Инв.№дубл.        | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | ckah-    | Kah- 20.04.2018 |      | 31918-3    |                   |              |      |  |  |  |

## 1 Описание и работа СБИС 1888ВВ018А

#### 1.1 Назначение СБИС 1888ВВ018А

Микросхема интегральная 1888ВВ018А (далее по тексту СБИС 1888ВВ018А) предназначена для организации обмена информацией по интерфейсу РСІ Express. СБИС 1888ВВ018А реализует функционал физического уровня интерфейса РСІ Express стандарта версии 1.1.

Интерфейс обмена данными с контроллером канального уровня интерфейса PCI Express соответствует требованиям Intel PHY Interface for PCI Express architecture v1.1 (PIPE 1.0).

Для выполнения данной задачи в СБИС 1888ВВ018А реализованы следующие функции:

- передача и прием данных со скоростью до 2 Гбит/сек по интерейсу PCI Express;

- восстановление данных и тактового сигнала из последовательного принимаемого потока стандарта PCI Express;

- преобразование передаваемых данных из параллельного вида в последовательныйы (сериализация);

- преобразование принимаемых данных из последовательного вида в параллельный (десериализация);

- кодирование передаваемых данных и декодирование принимаемых в соответствии с 8b/10b кодировкой;

- буферизация передаваемых данных и адаптивная буферизация для входных данных;

- выравнивание принимаемых данных в соответствии с требованиями интерфейса с канальным уровнем PIPE 1.0;

- организация обмена данными с канальным уровнем в соответствии с требованиями Intel PHY Interface for PCI Express architecture v1.1 (PIPE 1.0);

- формирование тактовых сигналов, необходимых для работы интерфейса PCI Express, с использованием внешнего опорного тактового сигнала;

Кроме этого в микросхеме реализован ряд дополнительных функций:

- определения наличия приемника на другой стороне соединения (Receiver detection);

- поддержка смены полярности линии;

- калибровка выходного сопротивления через внешний резистор для компенсации технологического разброса параметров микросхемы;

- поддержка внешнего входного тактового сигнала для синхронизации входных данных интерфейса PIPE1.0;

- поддержка режима петли обратной связи (loopback) со встроенной схемой диагностики соединения;

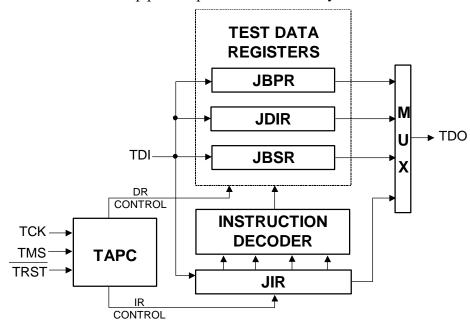

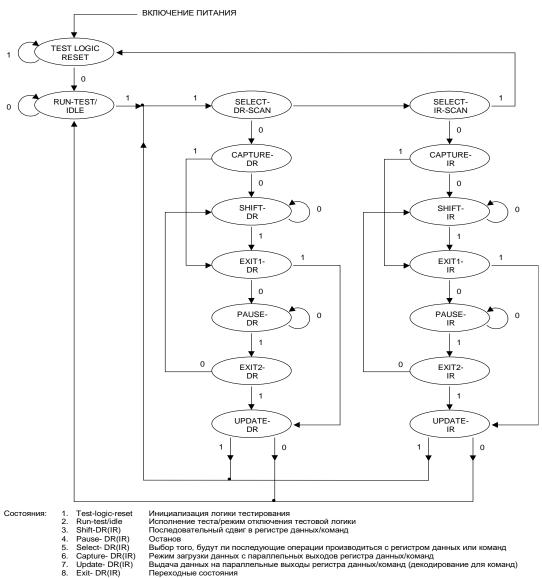

- поддержка отладочного интерфейса JTAG для диагностики состояния микросхемы, работы встроенной системы самотестирования и

|      |         |          |          |      |            |                 |              | Лист |  |  |  |

|------|---------|----------|----------|------|------------|-----------------|--------------|------|--|--|--|

|      |         |          |          |      | 1          | ЮФКВ.431268.019 | 9PЭ          | 4    |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                 |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                 |              |      |  |  |  |

периферийного сканирования выводов параллельного интерфейса с канальным уровнем по протоколу JTAG IEEE 1149.1.

## 1.2 Основные характеристики СБИС 1888ВВ018А

В данном разделе приводятся основные характеристики, дающие представление об особенностях микросхемы

- Совместимость с PCI Express Base Specification 1.1;

- Пропускная способность канала до 2Гб/сек.;

- Интерфейс с контроллером канального уровня в соответствии с требованиями Intel PHY Interface for PCI Express architecture (PIPE 1.0)

- 16 разрядные шины записи и чтения с тактовой частотой передачи 125МГп.:

- SSTL-1.8 буфера ввода/вывода шины интерфейса связи с контроллером канального уровня;

- Поддержка калибровки выходного сопротивления линии с помощью внешнего резистора сопротивлением  $1 \text{кOm} \pm 1\%$ ;

- Встроенная функция определения наличия приемника на линии;

- Поддержка смены полярности линии;

- Поддержка прямого управления диспаритетом передаваемого байта;

- Наличие JTAG интерфейса (IEEE 1149.1);

- Встроенная система тестирования с внутренней петлей обратной связи;

- CMOS 3.3В буфера ввода/вывода выводов системы тестирования и JTAG интерфейса;

- Дифференциальный вход генератора внешнего тактового сигнала частоты 100МГц. ±300 ppm.;

- Собственная потребляемая мощность не более 0,8 Вт.

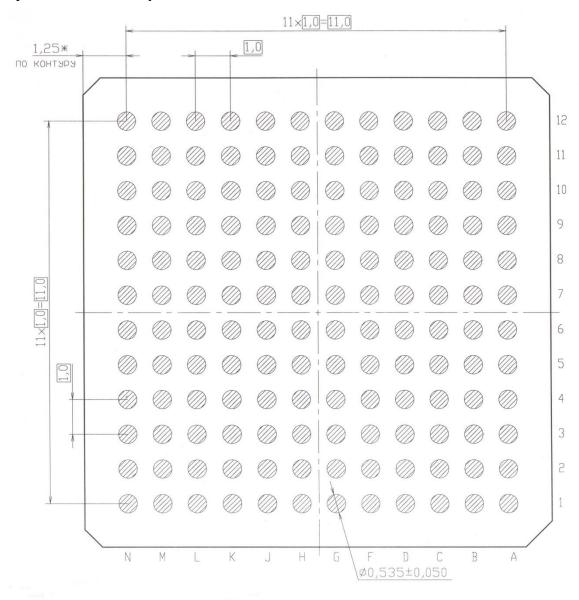

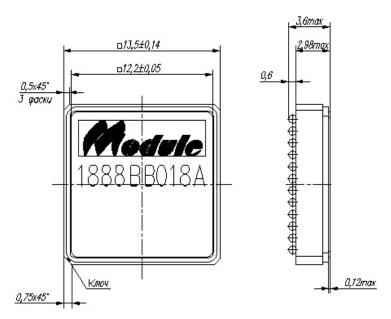

- Металлокерамический корпус типа CBGA (Ceramic Bold Grid Array) 144 вывода с шагом расположения выводов 1мм.

- Габариты корпуса не более:  $13.5 \times 13.5 \times 3.6$  мм;

- Температурный диапазон работы микросхемы -60°C +85°C.

|      |         |          |          |      |            |                   |              | Лист |  |  |  |

|------|---------|----------|----------|------|------------|-------------------|--------------|------|--|--|--|

|      |         |          |          |      |            | ЮФКВ.431268.019РЭ |              |      |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                   |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.        | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                   |              |      |  |  |  |

## 1.3 Структурная схема СБИС 1888ВВ018А

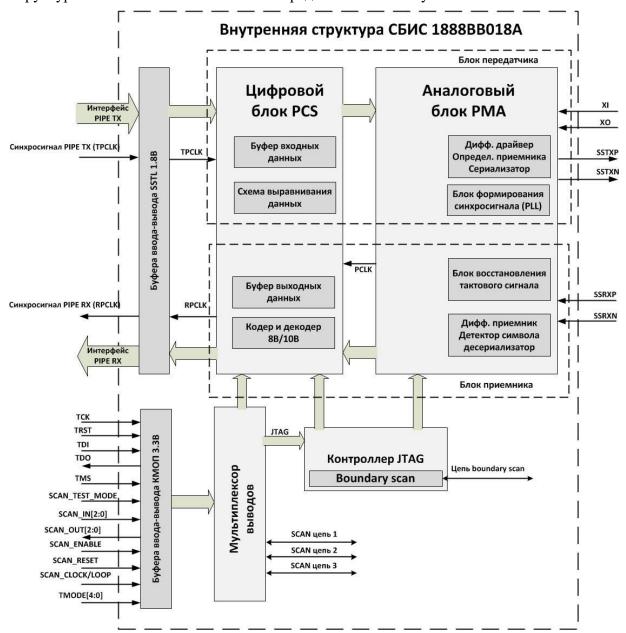

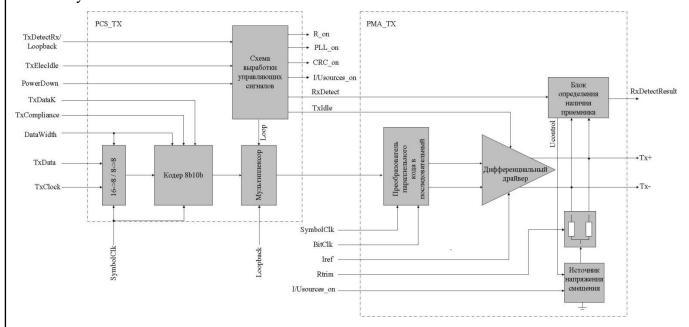

Структурная схема СБИС 1888ВВ018А представлена на Рисунок 1.1.

Рисунок 1.1 – Обобщенная структурная схема СБИС 1888ВВ018А

СБИС 1888ВВ018А структурно состоит из приемной и передающей частей, а также дополнительного оборудования, выполняющего вспомогательные функции канала и проверку работоспособности оконечного оборудования канала РСІ Express в составе изделия.

|      |         |          |          |      |            |                 |              | Лист |  |  |  |

|------|---------|----------|----------|------|------------|-----------------|--------------|------|--|--|--|

|      |         |          |          |      |            | ЮФКВ.431268.019 | 9PЭ          | 6    |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                 |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                 |              |      |  |  |  |

#### В состав приемной части СБИС 1888ВВ018А входят:

- дифференциальный входной драйвер приемника данных по интерфейсу PCI Express;

- блок восстановления тактового сигнала;

- блок восстановления данных;

- преобразователь последовательного кода в параллельный;

- детектор символа К28.5;

- адаптивный входной буфер данных с функцией компенсации разницы опорных частот приемника и передатчика;

- декодер 8b/10b;

- блок формирования кода состояния.

### В состав передающей части СБИС 1888ВВ018А входят:

- буфер передаваемых данных;

- кодер 8b/10b;

- преобразователь параллельного кода в последовательный;

- схема выработки управляющих сигналов;

- дифференциальный драйвер передатчика;

- блок определения наличия приемника;

- блок формирования синхросигнала.

#### К дополнительному оборудованию СБИС 1888ВВ018А относятся:

- мультиплексор выводов управления сканирующими цепями;

- контроллер JTAG-интерфейса по стандарту IEEE 1149.1;

- сканирующие цепи СБИС.

Функциональное описание работы основных внутренних узлов и блоков СБИС 1888ВВ018А приведено в разделе 1.4 данного руководства по эксплуатации.

|      |         |          |          |      |            |                   |              | Лист |  |  |  |

|------|---------|----------|----------|------|------------|-------------------|--------------|------|--|--|--|

|      |         |          |          |      | ŀ          | ЮФКВ.431268.019РЭ |              |      |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                   |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.        | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                   |              |      |  |  |  |

# 1.4 Внешние выводы СБИС 1888ВВ018А

СБИС 1888ВВ018А имеет 80 функциональных выводов, назначение которых приведено в Таблица 1.1.

Таблица 1.1 - Функциональные выводы СБИС 1888ВВ018А

| Обозначение <sup>1)</sup> | Кол-во                                                 | <b>Тип<sup>2</sup></b> | Функциональное назначение                                                                           |  |  |

|---------------------------|--------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------|--|--|

| Интер                     |                                                        |                        | ллером канального уровня - PIPE 1.0 (51 вывод)<br>уферов ввода/вывода – SSTL-1.8                    |  |  |

|                           |                                                        |                        | Интерфейс с приемником                                                                              |  |  |

| RPCLK                     | 1                                                      | О                      | Выходной тактовый сигнал интерфейса РІРЕ                                                            |  |  |

| RX_DATA[15:0]             | 16                                                     | О                      | Выходная шина данных приемника                                                                      |  |  |

| RX_DATAK[1:0]             | 2                                                      | О                      | Индикаторы контрольных символов на выходной шине приемника                                          |  |  |

| RX_STATUS[2:0]            | 3                                                      | О                      | Выходная шина кода состояния приемной части интерфейса PCI Express                                  |  |  |

| RX_VALID                  | 1                                                      | О                      | Сигнал – индикатор достоверности данных на шине приемника                                           |  |  |

| RX_POLARITY               | 1                                                      | I                      | Управление полярностью линии приемника PCI Express                                                  |  |  |

| RX_ELEC_IDLE              | 1                                                      | О                      | Индикация состояния холостого хода приемника                                                        |  |  |

| Интерфейс с передатчиком  |                                                        |                        |                                                                                                     |  |  |

| TPCLK                     | 1                                                      | I                      | Входной тактовый сигнал интерфейса РІРЕ                                                             |  |  |

| TX_DATA[15:0]             | 16                                                     | I                      | Входная шина данных передатчика                                                                     |  |  |

| TX_DATAK[1:0]             | 2                                                      | I                      | Индикаторы контрольных символов на входной шине данных передатчика                                  |  |  |

| TX_COMPLIANCE             | 1                                                      | I                      | Установка отрицательного диспаритета при передаче нулевого байта данных на входной шине передатчика |  |  |

| TX_DETECT_RX              | 1                                                      | I                      | Управления процедурой определения приемника.                                                        |  |  |

| TX_ELEC_IDLE              | 1                                                      | I                      | Управления режимом холостого хода дифференциального передатчика                                     |  |  |

|                           | (                                                      | Обще                   | е управление приемопередатчиком                                                                     |  |  |

| POWER_<br>DOWN[1:0]       | 2                                                      | I                      | Управление режимами пониженного потребления приемопередатчика                                       |  |  |

| RESETn                    | 1                                                      | I                      | Сигнал общего асинхронного сброса приемника и передатчика                                           |  |  |

| PHY_STATUS                | Сигнал индикации завершения переходов между различными |                        |                                                                                                     |  |  |

|      |         |          |          |      |            |                   |              | Лист |  |  |  |

|------|---------|----------|----------|------|------------|-------------------|--------------|------|--|--|--|

|      |         |          |          |      | 1          | ЮФКВ.431268.019РЭ |              |      |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                   |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.        | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                   |              |      |  |  |  |

Таблица 1.1 - Функциональные выводы СБИС 1888ВВ018А (продолжение)

| Обозначение 1) | Кол- | Тип <sup>2</sup> | Функциональное назначение                                 |

|----------------|------|------------------|-----------------------------------------------------------|

|                | ВО   | )                |                                                           |

|                | Вы   | іводы            | интерфейса PCI Express (7 выводов)                        |

| SSTXP, SSTXN   | 2    | О                | Дифференциальный выход передатчика PCI Express            |

| SSRXP, SSRXN   | 2    | I                | Дифференциальный вход приемника PCI Express               |

| XP,XN          | 2    | I                | Дифференциальный вход источника опорной частоты           |

| AF,AIN         |      | 1                | стандарта PCI Express (HCSL) – 100МГц.                    |

| REXT           | 1    | Α                | Вывод для подключения калибровочного резистора            |

| KLAT           | 1    | Λ                | $Re = 1$ к $O$ м $\pm 1$ %                                |

|                |      |                  | Интерфейс JTAG (6 выводов)                                |

|                | 7    | Гип бу           | уферов ввода/вывода – CMOS-3.3                            |

| TCK            | 1    | I                | Тактовый сигнал тестового интерфейса                      |

| TRSTn          | 1    | I                | Асинхронный сброс тестового порта                         |

| TDI            | 1    | I                | Вход тестовых данных                                      |

| TDO            | 1    | O                | Выход тестовых данных                                     |

| TMS            | 1    | I                | Выбор режима тестирования                                 |

| JTAG_EN        | 1    | I                | Асинхронный сигнал разрешения работы интерфейса JTAG.     |

|                | Te   | стовы            | іе выводы микросхемы (16 выводов)                         |

|                |      | Гип бу           | уферов ввода/вывода – CMOS-3.3                            |

| VSP_MODE[4:0]  | 5    | I                | Шина выбора тестового режима                              |

| VSP_RESETn     | 1    | I                | Асинхронный сброс тестовых схем                           |

| VSP_STXRXn     | 1    | I                | Сигнал включения внутренней аналоговой петли (передатчик  |

| VSP_STARAII    | 1    | 1                | замкнут на приемник)                                      |

| SCAN_TEST_MOD  | 1    | I                | Сигнал разрешения работы тестового сканирующего режима.   |

| VSP_TST_0      | 1    | I                | Сигнал разрешения сдвига данных (shift enable) в тестовом |

| VSF_1S1_0      | 1    | 1                | сканирующем режиме                                        |

| VSP_TST_1      | 1    | I                | Сигнал асинхронного сброса (scan reset) в тестовом        |

| 491_191_1      | _    | 1                | сканирующем режиме                                        |

| SCAN_IN[2:0]   | 3    | I                | Входы данных сканирующих цепочек                          |

| SCAN_OUT[2:0]  | 3    | О                | Выходы данных сканирующих цепочек                         |

#### Примечания:

- 1) Для обозначения выводов с активным низким уровнем сигнала в качестве последнего символа мени используется «n».

- 2) Используемые обозначения типов выводов:

I – вход,

O – выход,

A — аналоговый вывод

|      |         |          |          |      |            |                 |              | Лист |  |  |  |

|------|---------|----------|----------|------|------------|-----------------|--------------|------|--|--|--|

|      |         |          |          |      |            | ЮФКВ.431268.019 | 9P <b>9</b>  | 9    |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                 |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                 |              |      |  |  |  |

### 1.5 Устройство и работа СБИС 1888ВВ018А

СБИС 1888ВВ018А условно можно разбить на следующие блоки:

- блок формирования тактовых сигналов

- приемник сигналов интерфейса PCI express

- передатчик сигналов интерфейса PCI express

- блок калибровки согласующих резисторов линии

- блок интерфейса с внешним контроллером канального уровня (РІРЕ 1.0)

- отладочный интерфейс JTAG

#### 1.5.1 Блок формирования тактовых сигналов

Блок формирования тактовых сигналов предназначен для формирования тактовых сигналов для передающего и приемного тракта СБИС 1888ВВ018А, а также для тактирования работы интерфейса с внешним контроллером.

На дифференциальный вход (XP, XN) СБИС 1888ВВ018А подаётся внешний опорный тактовый сигнал частотой 100 МГц, который используется для формирования:

- тактового сигнала с частотой 2.5 ГГц  $\pm$  300 ppm для передачи данных;

- тактового сигнала с частотой 250 МГц  $\pm$  300 ppm для считывания принятых данных из буфера компенсации.

- тактового сигнала с частотой 125 МГц для тактирования работы интерфейса с внешним контроллером.

Тактовый сигнал 2.5 ГГц формируется умножителем частоты (PLL) синфазно с опорным тактовым сигналом СБИС. Остальные тактовые сигналы формируются делением тактового сигнала частоты 2.5 ГГп. На 10 и 20 соответственно.

#### 1.5.2 Блок приемника сигналов интерфейса PCI Express

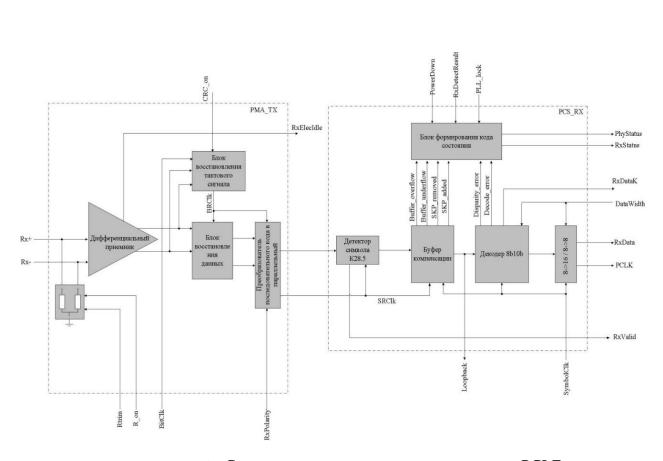

Структурная схема блока приемника сигналов интерфейса PCI Express представлена на Рисунок 1.2.

В состав блока приемника сигналов интерфейса PCI Express входят:

- блок дифференциального приёмника

- блок восстановления данных и тактового сигнала

- блок преобразования последовательного кода в параллельный (десериализатор)

- блок детектора символа К28.5

- буфер компенсации разницы опорных частот приемника и передатчика

- блок декодера 10b/8b

- блок управления и формирования состояния приемника

|      |         |          |          |      |            |                 |              | Лист |  |  |  |

|------|---------|----------|----------|------|------------|-----------------|--------------|------|--|--|--|

|      |         |          |          |      |            | ЮФКВ.431268.019 | )PЭ          | 10   |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                 |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |  |  |  |

| 3′   | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                 |              |      |  |  |  |

Pucyнok 1.2 – Структурная схема приемника сигналов PCI Express

#### 1.5.2.1 Блок дифференциального приемника

Дифференциальный приемник служит для предварительного усиления поступающего из линии передачи дифференциального сигнала, а также для детектирования состояния ожидания в линии по размаху входного сигнала.

Функцию предварительного усиления дифференциального сигнала выполняет дифференциальный каскад с резистивной нагрузкой. Перед подачей на вход усилителя, принятый сигнал сдвигается по уровню вверх при помощи схемы сдвига уровня.

Схема детектирования состояния ожидания сравнивает размах принимаемого сигнала с опорным уровнем сигнала. Если размах принимаемого сигнала менее 65 мВ, то схема детектирования формирует сигнал на внешнем выводе микросхемы RX\_ELEC\_IDLE об отключении передатчика от линии. Результат работы схемы детектирования представлен в Таблица 1.2.

|      |         |          |          |      |            |                   |              | Лист |  |  |  |

|------|---------|----------|----------|------|------------|-------------------|--------------|------|--|--|--|

|      |         |          |          |      | 1          | ЮФКВ.431268.019РЭ |              |      |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                   |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.        | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                   |              |      |  |  |  |

Таблица 1.2 - Результат работы схемы детектирования состояния ожидания

| Внешний вывод | Функциональное назначение    | Описание |                            |  |  |

|---------------|------------------------------|----------|----------------------------|--|--|

| RX_ELEC_IDLE  | Индикация состояния ожидания | 0 -      | Линия в активном состоянии |  |  |

|               |                              | 1 -      | Линия в состоянии ожидания |  |  |

#### 1.5.2.2 Блок восстановления данных и тактового сигнала

Блок CDR предназначен для восстановления тактового сигнала передатчика из принимаемого потока, фиксации по восстановленному тактовому сигналу значения передаваемых данных и формирования мультифазного дифференциального тактового сигнала для блока десериализатора.

Тактовый сигнал восстанавливается схемой на основе умножителя частоты (PLL) с нелинейным фазовым компаратором (bang-bang) на входе.

# 1.5.2.3 Блок преобразования последовательного кода в параллельный (десериализатор)

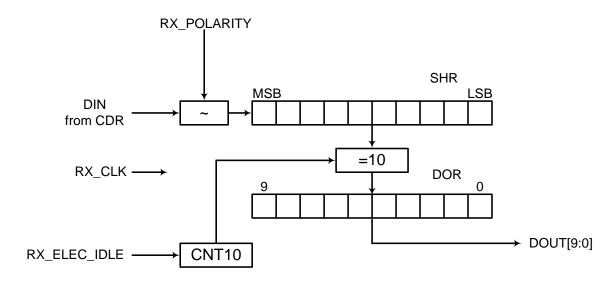

Структурная схема блока преобразования последовательного кода в параллельный (десериализатора) представлена на рисунке Рисунок 1.3.

Рисунок 1.3 -Структурная схема блока десериализатора

Блок преобразования последовательного кода в параллельный тактируется восстановленным тактовым сигналом RX\_CLK.

Для десериализации входного последовательного потока данных используется сдвиговый регистр SHR. Данные на вход блока поступают с блока восстановления тактового сигнала с частотой 2,5 ГГц. Так как длина передаваемого символа составляет 10 бит, каждые 10

|      |         |                  |       |         |                   |            |              | Лист |  |  |

|------|---------|------------------|-------|---------|-------------------|------------|--------------|------|--|--|

|      |         |                  |       |         | ЮФКВ.431268.019РЭ |            |              |      |  |  |

| Изм. | Лист    | № докум.         | Подп. | Дата    |                   |            |              |      |  |  |

| Инв  | .№подл. | Подп. и дата     |       |         | Взам.инв.№        | Инв.№дубл. | Подп. и дата |      |  |  |

| 3    | 1918-4  | Kahi- 20.04.2018 |       | 31918-3 |                   |            |              |      |  |  |

тактов, отсчитываемых управляющим счетчиком, данные из сдвигового регистра переписываюся в выходной регистр данных DOR. Частота выходного потока данных, таким образом, уменьшается в 10 раз до 250 МГц.

Управляющий сигнал RX\_ELEC\_IDLE обнуляет управляющий счетчик в случае, когда линия находится в состоянии ожидания.

Поскольку, в соответствии со спецификацией PCI Express<sup>TM</sup> Base Specification Revision 1.1, физический уровень PCI Express должен иметь возможность менять полярность входного сигнала, на вход блока подается сигнал с внешнего вывода RX\_POLARITY, который инвертирует данные перед их поступлением в сдвиговый регистр.

Порядок работы блока, в зависимости от состояния внешнего вывода RX\_POLARITY представлен в Таблица 1.3

Таблица 1.3 - Порядок работы блока десериализатора, в зависимости от состояния внешнего вывода RX POLARITY.

| Внешний вывод | Функциональное              |     | Описание                           |

|---------------|-----------------------------|-----|------------------------------------|

|               | назначение                  |     |                                    |

| RX_POLARITY   | Управление полярностью      | 0 – | Полярность данных не инвертируется |

|               | линии приемника PCI Express | 1 - | Полярность данных инвертируется    |

#### 1.5.2.4 Блок детектора символа К28.5

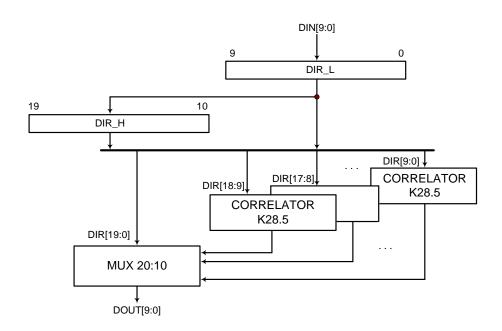

Блок детектора символа K28.5 предназначен для выравнивания данных, полученных из блока десериализатора. Выравнивание данных производится путем поиска первого символа данных, передаваемого при инициализации линии — символа K28.5. Структурная схема блока представлена на Рисунок 1.4.

Входные 10-разрядные данные запоминаются в младших разрядах входного 20разрядного регистра DIR. При поступлении новых данных, предыдущие сдвигаются в старшие разряды регистра DIR.

Из регистра DIR на идентичные друг другу корреляторы, сравнивающие входные данные и код управляющего символа K28.5, подаются разряды данных со сдвигом на один разряд. Выходы корреляторов управляют выходным мультиплексором, предназначенным для выравнивания данных, поступающих на буфер компенсации разницы опорных частот приемника и передатчика.

|      |         |                |       |            |            |              |  | Лист |  |  |

|------|---------|----------------|-------|------------|------------|--------------|--|------|--|--|

|      |         |                |       |            | 1          | 13           |  |      |  |  |

| Изм. | Лист    | № докум.       | Подп. | Дата       |            |              |  |      |  |  |

| Инв  | .№подл. | Подп. и дата   |       | Взам.инв.№ | Инв.№дубл. | Подп. и дата |  |      |  |  |

| 3    | 1918-4  | Mah 20.04.2018 |       |            | 31918-3    |              |  |      |  |  |

Рисунок 1.4 – Структурная схема блока детектора символа К28.5

#### 1.5.2.5 Буфер компенсации разницы опорных частот приемника и передатчика

Буфер компенсации разницы опорных частот приемника и передатчика (elastic buffer) используется при переходе тактирования с восстановленной из потока данных частоты передатчика на внутреннюю частоту приемника.

Данный буфер компенсирует разброс частот приемника и передатчика, возникающий изза разброса параметров и условий работы тактовых генераторов, соответственно приемника и передатчика. Эта компенсация осуществляется при помощи специальных символов (SKP символов), вставляемых непосредственно в поток данных.

Буфер компенсации представляет собой буфер данных магазинного типа (FIFO) с некоторыми особенностями управления операциями чтения. При появлении на выходе буфера SKP символа операция чтения из буфера зависит от заполненности буфера. Если буфер заполнен менее чем наполовину, то SKP символ считывается два раза, т.е. как бы вставляется в поток выходных данных. Если буфер заполнен более чем наполовину, то SKP символ игнорируется, т.е. убирается из потока выходных данных.

#### **1.5.2.6** Блок декодера 10b/8b

Блок декодера 8b/10b предназначен для декодирования 10-разрядного кода в 8-разрядную последовательность данных и реализован в соответствии со стандартом ANSI X3.230-1994.

Декодирование осуществляется следующим образом: 10-разрядное слово данных, считанное из буфера компенсации, разбивается на два блока — 4-разрядный (разряды 3:0) и 6- разрядный (разряды 9:4). Затем, для каждого из этих блоков осуществляется

|      |         |          |          |      |                   |            |              | Лист |  |  |  |

|------|---------|----------|----------|------|-------------------|------------|--------------|------|--|--|--|

|      |         |          |          |      | ЮФКВ.431268.019РЭ |            |              |      |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |                   |            |              |      |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№        | Инв.№дубл. | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3           |            |              | 1    |  |  |  |

табличное преобразование в 3-разрядный и 5-разрядный, соответственно. Полученные блоки меняются местами и объединяются в один 8-разрядный байт данных.

При получении некорректной 10-разрядной входной последовательности вырабатывается сигнал ошибки данных. Некорректными считаются следующие последовательности:

- 6-разрядный блок содержит более четырех единичных или нулевых разрядов;

- 4-разрядный блок содержит более трех единичных или нулевых разрядов;

- 10-разрядный блок содержит более шести единичных или нулевых разрядов;

- 10-разрядный блок содержит более пяти последовательных единичных или последовательных нулевых разрядов;

- 10-разрядный блок не может быть декодирован в корректную 8-разрядную последовательность.

В процессе преобразования производится восстановление значения текущего динамического дисбаланса нулевых и единичных битов декодированного байта данных и сравнение его с ожидаемым значением. В случае несовпадения ожидаемого и восстановленного значений вырабатывается сигнал ошибки динамического дисбаланса.

Принципы кодирования/декодирования описываются в разделе 4.2.1 и приложении В спецификации PCI Express Base Specification Revision 1.1.

#### 1.5.2.7 Блок управления и формирования состояния приемника

Блок управления и формирования состояния приемника управляет приемом данных, осуществляет обмен данными с передающей частью интерфейса PIPE и формирует коды состояния приемника и коды ошибок при приеме данных.

|      |         |                 |       |      |            |                 |              | Лист |  |  |

|------|---------|-----------------|-------|------|------------|-----------------|--------------|------|--|--|

|      |         |                 |       |      |            | ЮФКВ.431268.019 | PЭ           | 15   |  |  |

| Изм. | Лист    | № докум.        | Подп. | Дата |            |                 |              |      |  |  |

| Инв  | .№подл. | Подп. и дата    |       |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |  |  |

| 3    | 1918-4  | Kah- 20.04.2018 |       |      | 31918-3    |                 |              |      |  |  |

#### 1.5.3 Блок передатчика сигналов интерфейса PCI Express

Структурная схема блока передатчика сигналов интерфейса PCI Express представлена на Рисунок 1.5.

Рисунок 1.5 -Структурная схема передатчика сигналов PCI Express

В состав блока передатчика сигналов интерфейса PCI Express входят:

- блок кодера 8b/10b

- блок преобразования параллельного кода в последовательный (сериализатор)

- блок дифференциального драйвера линии

- блок определения наличия приемника

- блок управления передатчика

#### 1.5.3.1 Блок кодера 8b/10b

Блок кодера 8b/10b предназначен для кодирования 8-разрядных данных в 10-разрядный код и реализован в соответствии со стандартом ANSI X3.230-1994.

Кодирование осуществляется следующим образом: 8-разрядный байт данных, содержащий данные или управляющее символ, разбивается на два блока — 3-разрядный (разряды 7:5) и 5-разрядный (разряды 4:0). Эти блоки меняются местами, и для каждого из них происходит табличное преобразование в 4-разрядный и 6-разрядный блок соответственно.

При преобразовании для каждого блока учитывается текущий динамический дисбаланс нулевых и единичных битов. Результирующий 10-разрядный блок данных получается объединением 4-разрядного и 6-разрядного блоков.

|      |         |              |          |      |                   |            |              | Лист |  |  |  |

|------|---------|--------------|----------|------|-------------------|------------|--------------|------|--|--|--|

|      |         |              |          |      | ЮФКВ.431268.019РЭ |            |              |      |  |  |  |

| Изм. | Лист    | № докум.     | Подп.    | Дата |                   |            |              |      |  |  |  |

| Инв  | .№подл. | Подп. и дата |          |      | Взам.инв.№        | Инв.№дубл. | Подп. и дата |      |  |  |  |

| 3    | 1918-4  | Kah-         | 20.04.20 | 18   | 31918-3           |            |              | 1    |  |  |  |

Принципы и таблицы кодирования/декодирования описываются в приложении В спецификации PCI Express Base Specification Revision 1.1.

# **1.5.3.2** Блок преобразования параллельного кода в последовательный (сериализатор)

Блок предназначен для преобразования полученного с блока кодера 10 разрядного слова данных в последовательный код.

Для преобразования используется 10 разрядный сдвиговый регистр. Так как запись в сдвиговый регистр и сдвиг данных тактируются синфазными тактовыми сигналами, задаваемыми блоком формирования тактовых сигналов (250МГц. и 2.5ГГц. соответственно), дополнительная буферизация данных не используется.

Считывание последовательных данных производится из младшего разряда сдвигового регистра (в соответствии со спецификацией PCI Express<sup>TM</sup> Base Specification Revision 1.1). Далее данные преобразуются в дифференциальную форму и подаются на блок дифференциального драйвера линии.

#### 1.5.3.3 Блок дифференциального драйвера линии

Блок дифференциального драйвера линии преобразует уровни сигнала, поступающего из блока сериализатора, до значений, требуемых спецификацией PCI Express<sup>TM</sup> Base Specification Revision 1.1, формирует сигнал на выводах микросхемы и в соответствии с управляющим сигналом вносит предискажения в выходной сигнал. Внесение предискажений в выходной сигнал уменьшает отражения и перекрестные помехи в канале связи.

#### 1.5.3.4 Блок определения наличия приемника

Блок определяет наличия или отсутствие наличия приемника на противоположном конце линии связи. Работа блока основывается на измерении времени нарастания перепада синфазного напряжения, подаваемого на выводы передатчика. При подключении приемника емкость, на которую работает передатчик, резко возрастает, за счет разделительной емкости и собственно емкости канала передачи. Соответственно увеличивается время нарастания сигнала при подаче на дифференциальные выходы передатчика положительных синфазных фронтов.

При запросе от блока управления на определение наличия приемника, блок определения наличия приемника сначала заземляет выводы передатчика (SSTXP и SSTXN), а затем выдает на них напряжение равное 500 мВ. Через время, равно 4 мкс компаратор блока сравнивает напряжение на выводах SSTXP и SSTXN с эталонным значением (400 мВ). Если напряжение на выводах SSTXP и SSTXN больше этого значения, то приемник отсутствует. Если напряжение на выводах SSTXP и SSTXN меньше, то приемник подключен к линии передачи.

Процедура обнаружения приемника задается с помощию внешнего вывода TX\_DETECT\_RX микросхемы. Результат процесса обнаружения приемника выдается на внешние выводы RX\_STATUS[2:0].

|      |         |              |          |      |            |                 |              | Лист |  |  |

|------|---------|--------------|----------|------|------------|-----------------|--------------|------|--|--|

|      |         |              |          |      | 1          | ЮФКВ.431268.019 | 9PЭ          | 17   |  |  |

| Изм. | Лист    | № докум.     | Подп.    | Дата |            |                 |              |      |  |  |

| Инв  | .№подл. | Подп. и дата |          |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |  |  |

| 3    | 1918-4  | Kah-         | 20.04.20 | 18   | 31918-3    |                 |              |      |  |  |

#### 1.5.3.5 Блок управления передатчика

Блок управления передатчика задает режимы работы передатчика, управляет передачей данных, осуществляет обмен данными с принимающей частью интерфейса PIPE и формирует коды состояния передатчика.

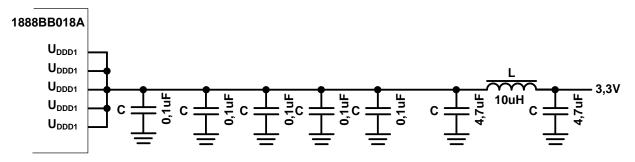

#### 1.5.4 Блок калибровки согласующих резисторов линии

Блок калибровки согласующих резисторов линии предназначен для компенсации технологического разброса параметров согласующих резисторов линии передачи данных.

Для реализации обмена данными по линии передачи, в соответствии со стандартом PCI Express, необходимы согласующие резисторы сопротивлением 50 Ом ( $\pm$  20) %. Технологический КМОП процесс не позволяет гарантированно изготовить резисторы с требуемой точностью. Поэтому применение блока калибровки является насущной необходимостью.

Так как параметры резисторов, изготовляемых по стандартному КМОП процессу, имеют значительный технологический разброс, то вместо одного согласующего резистора изготовляется линейка резисторов разных номиналов, каждый из которых может быть подключен к линии аналоговым ключом. Выбор количества и номинала резисторов для подключения осуществляется путем сравнения напряжения встроенного опорного источника питания с напряжением на резистивном делителе. Одним плечом делителя является высокоточный внешний резистор  $R_e$  номиналом  $1 \kappa Om \pm 1\%$ , подключаемый к внешнему выводу REXT микросхемы. Вторым плечом делителя является встроенная линейка резисторов аналогичная используемой для согласования линии передачи.

В процессе калибровки происходит перебор подключения резисторов линейки к делителю таким образом, чтобы напряжение на делителе совпало с опорным напряжением. После совпадения количество и порядок резисторов, подключенных к делителю, задают код, управляющий подключением набора согласующих резисторов к линии. Калибровка производится при подаче низкого уровня на вход RESETn.

#### 1.5.5 Блок интерфейса с внешним контроллером канального уровня (РІРЕ 1.0)

СБИС 1888ВВ018А поддерживает работу интерфейса с канальным уровнем PIPE в соответствии со стандартом Intel PHY Interface for PCI Express architecture PIPE 1.0. Поддержка данного стандарта позволяет обеспечить совместимость СБИС 1888ВВ018А с любыми стандартными контроллерами канального уровня интерфейса PCI Express.

В качестве электрического стандарта для обмена данными по интерфейсу PIPE используется стандарт SSTL с напряжением  $1.8 \pm 0.15$  B.

#### 1.5.5.1 Функциональные выводы интерфейса

Функциональное назначение выводов интерфейса с канальным уровнем представлено в Таблица 1.4.

|      |         |                 |       |      |            |                 |              | Лист |  |  |

|------|---------|-----------------|-------|------|------------|-----------------|--------------|------|--|--|

|      |         |                 |       |      | ŀ          | ОФКВ.431268.019 | 9PЭ          | 18   |  |  |

| Изм. | Лист    | № докум.        | Подп. | Дата |            |                 |              |      |  |  |

| Инв  | .№подл. | Подп. и дата    |       |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |  |  |

| 3    | 1918-4  | Kah- 20.04.2018 |       |      | 31918-3    |                 |              |      |  |  |

Таблица 1.4 - Функциональные выводы интерфейса с канальным уровнем

| Обозначение 1)           | Кол-во                                       | <b>Тип<sup>2</sup></b> | Функциональное назначение                                                                                                                            |  |  |  |  |  |

|--------------------------|----------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                          |                                              |                        | Интерфейс с приемником                                                                                                                               |  |  |  |  |  |

| RPCLK                    | 1                                            | О                      | Выходной тактовый сигнал интерфейса РІРЕ                                                                                                             |  |  |  |  |  |

| RX_DATA[15:0]            | 16                                           | О                      | Выходная шина данных приемника                                                                                                                       |  |  |  |  |  |

| RX_DATAK[1:0]            | 2                                            | О                      | Индикаторы контрольных символов на выходной шине приемника                                                                                           |  |  |  |  |  |

| RX_STATUS[2:0]           | 3                                            | 0                      | Выходная шина кода состояния приемной части интерфейса PCI Express                                                                                   |  |  |  |  |  |

| RX_VALID                 | 1                                            | О                      | Сигнал – индикатор достоверности данных на шине приемника                                                                                            |  |  |  |  |  |

| RX_POLARITY              | 1                                            | I                      | Управление полярностью линии приемника PCI Express                                                                                                   |  |  |  |  |  |

| RX_ELEC_IDLE             | 1                                            | О                      | Индикация состояния холостого хода приемника                                                                                                         |  |  |  |  |  |

| Интерфейс с передатчиком |                                              |                        |                                                                                                                                                      |  |  |  |  |  |

| TPCLK                    | 1                                            | I                      | Входной тактовый сигнал интерфейса РІРЕ                                                                                                              |  |  |  |  |  |

| TX_DATA[15:0]            | 16                                           | I                      | Входная шина данных передатчика                                                                                                                      |  |  |  |  |  |

| TX_DATAK[1:0]            | 2                                            | Ι                      | Индикаторы контрольных символов на входной шине данных передатчика                                                                                   |  |  |  |  |  |

| TX_COMPLIANC<br>E        | 1                                            | I                      | Установка отрицательного диспаритета при передаче нулевого байта данных на входной шине передатчика                                                  |  |  |  |  |  |

| TX_DETECT_RX             | 1                                            | I                      | Управления процедурой определения приемника.                                                                                                         |  |  |  |  |  |

| TX_ELEC_IDLE             | 1                                            | I                      | Управления режимом холостого хода дифференциального передатчика                                                                                      |  |  |  |  |  |

|                          | (                                            | Эбщее                  | управление приемопередатчиком                                                                                                                        |  |  |  |  |  |

| POWER_<br>DOWN[1:0]      | 2                                            | I                      | Управление режимами пониженного потребления приемопередатчика                                                                                        |  |  |  |  |  |

| RESETn                   | Сигнал общего зещуронного сброса приминиза и |                        |                                                                                                                                                      |  |  |  |  |  |

| PHY_STATUS               | 1                                            | О                      | Сигнал индикации завершения переходов между различными состояниями пониженного энергопотребления, а также завершения процедуры обнаружения приемника |  |  |  |  |  |

Примечания:

I – вход,

О – выход,

#### 1.5.5.2 Тактовые сигналы интерфейса

Для работы интерфейса с канальным уровнем в СБИС 1888ВВ018А используется два синхросигнала. Синхросигнал RPCLK с частотой 125МГЦ вырабатывается внутри СБИС 1888ВВ018А и используется для тактирования выходных сигналов интерфейса с канальным уровнем.

|      |         |                 |       |      |            |            |              | Лист |  |  |

|------|---------|-----------------|-------|------|------------|------------|--------------|------|--|--|

|      |         |                 |       |      |            | 19         |              |      |  |  |

| Изм. | Лист    | № докум.        | Подп. | Дата |            |            |              |      |  |  |

| Инв  | .№подл. | Подп. и дата    |       |      | Взам.инв.№ | Инв.№дубл. | Подп. и дата |      |  |  |

| 3    | 1918-4  | Kah- 20.04.2018 |       |      | 31918-3    |            |              |      |  |  |

<sup>1) -</sup> Для обозначения выводов с активным низким уровнем сигнала в качестве последнего символа мени используется «n».

<sup>2) -</sup> Используемые обозначения типов выводов:

Синхросигнал ТРСLК является внешним сигналом. Данный синхросигнал тактирует работу входных сигналов интерфейса. Этот синхросигнал должен быть синхронен RPCLK, т.е. повторять сигнал RPCLK со сдвигом фазы. Обычно это достигается подключением сигнала ТРСLК к сигналу RPCLK на печатной плате или внутри контроллера канального уровня.

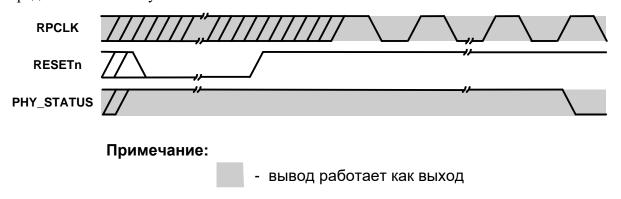

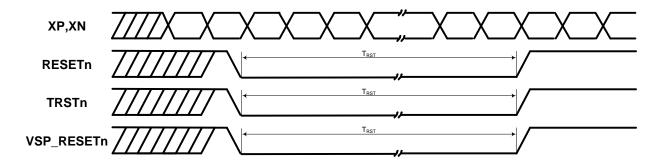

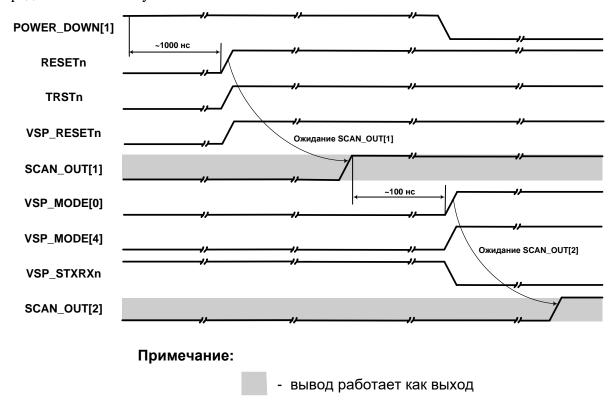

#### 1.5.5.3 Сигнал асинхронного сброса

В начале работы, а также при выходе из режима сверхнизкого энергопотребления P2, на вход RESETn необходимо подать сигнал асинхронного сброса (активный уровень низкий) длительностью не менее 100 мкс. Длительность 100 мкс отсчитывается от момента, когда все входные напряжения питания и опорный тактовый дифференциальный сигнал (XP, XN - 100МГц) вышли на рабочий режим и стабильны.

В начале работы одновременно необходимо подать сигнал асинхронного сброса длительностью 100 мкс и на внешние выводы TRSTn и VSP\_RESETn. Допускается подача сигнала сброса от одного источника одновременно на все три входа.

При активном уровне сигнала RESETn необходимо, чтобы на управляющие входы СБИС 1888ВВ018Ф были установлены в следующие состояния:

TX\_ELEC\_IDLE – в лог. 1

$RX_POLARITY - в лог. 0$

$TX_DETECT_RX - в лог. 0$

$TX_COMPLIANCE - в лог. 0$

POWER\_DOWN[1:0] – в состояние 10b

После снятия сигнала сброса происходит установка рабочего режима встроенного умножителя частоты (PLL) и калибровка согласующих резисторов линии передачи. Индикатором готовности микросхемы к работе является появление сигнала низкого уровня на выходе PHY\_STATUS. Временная диаграмма подачи сигнала сброса представлена на Рисунок 1.6.

Рисунок 1.6-Временная диаграмма подачи сигнала сброса

|      |         |                 |       |      |                   |            |              | Лист |  |  |

|------|---------|-----------------|-------|------|-------------------|------------|--------------|------|--|--|

|      |         |                 |       |      | ЮФКВ.431268.019РЭ |            |              |      |  |  |

| Изм. | Лист    | № докум.        | Подп. | Дата |                   |            |              |      |  |  |

| Инв  | .№подл. | Подп. и дата    |       |      | Взам.инв.№        | Инв.№дубл. | Подп. и дата |      |  |  |

| 3    | 1918-4  | Kah- 20.04.2018 |       |      | 31918-3           |            |              |      |  |  |

#### 1.5.5.4 Режимы знергопотребления микросхемы

В соответствии со стандартом РІРЕ, СБИС 1888ВВ018А поддерживает 4 режима работы:

- РО стандартный режим работы микросхемы. В данном режиме активны все внешние и внутренние синхросигналы, микросхема готова к приему и передаче данных по интерфейсам РІРЕ и PCI Express.

- P0s режим пониженного энергопотребления. В данном режиме СБИС 1888ВВ018А находится в режиме ожидания данных, передатчик при этом находится в состоянии холостого хода (electrical idle). Выход из режима инициируется при поступлении входных данных на приемник PCI Express, либо при изменении состояния на выводах POWER\_DOWN[1:0] микросхемы. В начале работы, после асинхронного сброса СБИС 1888ВВ018А, должна находиться в данном режиме.

- P1 режим низкого энергопотребления. В данном режиме приемник отключен, передатчик находится в состоянии холостого хода (electrical idle). Передача и прием данных по интерфейсу PCI Express невозможны. Тактовый сигнал интерфейса PIPE (RPCLK) активен. Выход из режима инициируется при изменении состояния на выводах POWER\_DOWN[1:0] микросхемы.

- Р2 режим сверхнизкого энергопотребления. В данном режиме отключается встроенный умножитель частоты (PLL). Тактовые сигналы не вырабатываются. Отключены приемник и передатчик. Выход из данного режима инициируется подачей на вход RESETn сигнала асинхронного сброса длительностью не менее 100 мкс и установкой при этом нужного состояния на шине POWER\_DOWN[1:0].

Режимы энергопотребления микросхемы задаются состоянием на управлеющих входах POWER\_DOWN[1:0]. Зависимость режима энергопотребления микросхемы от состояния на входах POWER\_DOWN[1:0] представлена в Таблица 1.5.

Таблица 1.5 - Зависимость режима энергопотребления микросхемы от состояния на входах *POWER\_DOWN*/.

| Внешний   | Функциональное                       | Описание                                       |

|-----------|--------------------------------------|------------------------------------------------|

| вывод     | назначение                           |                                                |

| POWER-    |                                      | 00 – Стандартный режим – Р0                    |

| DOWN[1:0] | энергопотребления СБИС<br>1888ВВ018А | 01 — Режим пониженного энергопотребления — P0s |

|           |                                      | 10 – Режим низкого энергопотребления – Р1      |

|           |                                      | 11 — Режим сверхнизкого энергопотребления — Р2 |

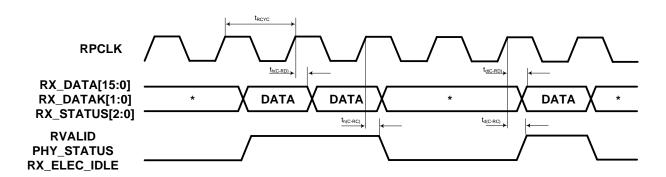

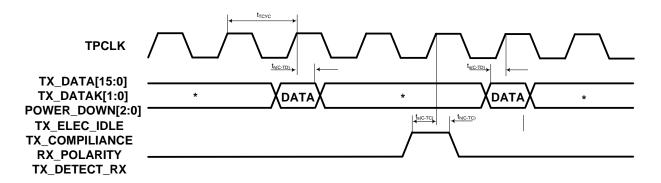

#### 1.5.5.5 Обмен информацией по интерфейсу РІРЕ

Передача данных между контроллером канального уровня и СБИС 1888ВВ018А осуществляется по двум 16-разрядным шинам.

|      |         |          |          |      |                   |            |              | Лист |  |

|------|---------|----------|----------|------|-------------------|------------|--------------|------|--|

|      |         |          |          |      | ЮФКВ.431268.019РЭ |            |              |      |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |                   |            |              |      |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№        | Инв.№дубл. | Подп. и дата |      |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3           |            |              |      |  |

По шине RX\_DATA[15:0] СБИС 1888ВВ018А передает контроллеру канального уровня принимаемые по интерфейсу РСІ Express данные. Причем байт данных RX\_DATA[7:0] был принят раньше байта данных RX\_DATA[15:8]. Передача данных стробируется сигналом RX VALID. Частота передачи данных - 125МГц.

По шине TX\_DATA[15:0] контроллер передает СБИС 1888ВВ018А передаваемые по интерфейсу PCI Express данные. Причем байт данных TX\_DATA[7:0] будет передан раньше байта данных TX\_DATA[15:8]. Данные защелкиваются во входных регистрах СБИС 1888ВВ018А по положительному фронту сигнала ТРСЬК. Частота передачи данных — 125МГц.

Каждый передаваемый и принимаемый байт сопровождается признаком, является ли этот байт символом данных или контрольным символом. Эти признаки выдаются на выводы RX\_DATAK[1:0] для шины приема и TX\_DATAK[1:0] для шины передачи. При этом контрольный признак RX\_DATAK[1] (TX\_DATAK[1]) относится к старшему байту шины, а признак RX\_DATAK[0] (TX\_DATAK[0]) соответственно к младшему. Тип передаваемого или принимаемого байта, в зависимости от состояния на выводах RX\_DATAK[1:0] (TX\_DATAK[1:0]) представлен в Таблица 1.6.

Таблица 1.6 - Тип передаваемого или принимаемого байта, в зависимости от состояния выводов RX\_DATAK[1:0] (TX\_DATAK[1:0]).

| Внешний вывод   | Функциональное        | Описание               |

|-----------------|-----------------------|------------------------|

|                 | назначение            |                        |

| RX_DATAK[1:0]   | Тип передаваемого или | 0 – Символ данных      |

| (TX_DATAK[1:0]) | принимаемого байта    | 1 - Контрольный символ |

В соответствии со стандартом Intel PHY Interface for PCI Express architecture PIPE 1.0. контроллер канального уровня должен задавать ряд операций и получать информацию о состоянии канала передачи и о наличии ошибок в принимаемом потоке данных. Данные процедуры задаются с помощью внешних выводов RX\_POLARITY, TX\_COMPLIANCE, TX\_DETECT\_RX, TX\_ELEC\_IDLE, а информация о состоянии выводится на внешние выводы RX\_ELEC\_IDLE и RX\_STATUS[2:0].

На внешний вывод RX\_ELEC\_IDLE выводится информация о состоянии линии приема, подключенной к СБИС 1888ВВ018А. Результат анализа состояния линии приема представлен в Таблица 1.7.

Таблица 1.7- Результат анализа состояния линии приема, подключенной к СБИС 1888ВВ018А

| Внешний вывод | Функциональное назначение    |     | Описание                   |

|---------------|------------------------------|-----|----------------------------|

| RX_ELEC_IDLE  | Индикация состояния ожидания | 0 - | Линия в активном состоянии |

|               |                              | 1 - | Линия в состоянии ожидания |

|      |         |          |          |      |            |                 |              | Лист |

|------|---------|----------|----------|------|------------|-----------------|--------------|------|

|      |         |          |          |      |            | ЮФКВ.431268.019 | )PЭ          | 22   |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                 |              | 22   |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |

| 3′   | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                 |              |      |

На внешние выводы RX\_STATUS[2:0] выводится результат операции обнаружения приемника и коды обнаруженных ошибок в принимаемом потоке данных. Кодировка ошибок при приеме данных представлена в Таблица 1.8.

Таблица 1.8 - Кодировка ошибок при приеме данных

| Внешний вывод  | Функциональное<br>назначение |                                    | Описание                                                                                                                                                                                                                                    |

|----------------|------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX_STATUS[2:0] |                              | ои 000<br>001<br>010<br>011<br>100 | 1 — Добавлен один символ (SKP) в адаптивный буфер для компенсации разброса частот приемника и передатчика 0 — Удален один символ (SKP) из адаптивного буфера для компенсации разброса частот приемника и передатчика 0 — Обнаружен приемник |

|                |                              | 110                                | 0 — Переполнение адаптивного буфера                                                                                                                                                                                                         |

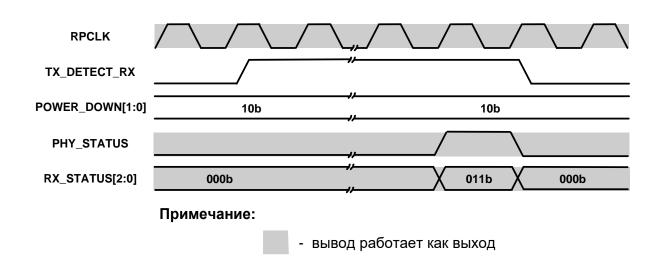

#### 1.5.5.5.1 Определение наличия приемника

Данная операция позволяет определить наличие подключенного к передатчику приемника интерфейса PCI Express. Операция выполняется при работе СБИС 1888ВВ018А в режиме низкого энергопотребления (P1). Для начала операции необходимо установить в логическую 1 входной сигнал TX\_DETECT\_RX. После окончания процесса определения приемника, СБИС 1888ВВ018А выдает логическую 1 на внешний вывод PHY\_STATUS. Одновременно с этим на внешние выводы RX\_STATUS[2:0] выдается код завершения операции. Код завершения операции может иметь следующие значения:

000b – приемник не обнаружен;

011b – приемник обнаружен, можно начинать установку соединения.

Временная диаграмма операции обнаружения приемника представлена на Рисунок 1.7.

|      |         |          |          |      |                   |            |              | Лист |

|------|---------|----------|----------|------|-------------------|------------|--------------|------|

|      |         |          |          |      | ЮФКВ.431268.019РЭ |            |              | 23   |

| Изм. | Лист    | № докум. | Подп.    | Дата |                   |            |              | 23   |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№        | Инв.№дубл. | Подп. и дата |      |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3           |            |              |      |

Рисунок 1.7 – Временная диаграмма операции определения приемника

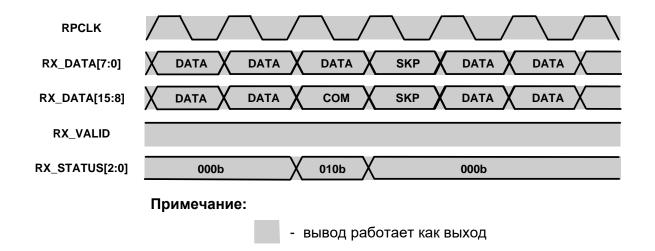

#### 1.5.5.5.2 Компенсация разницы частот передатчика и приемника PCI Express

Для компенсации разницы частот передатчика и приемника в передаваемый поток данных вставляются синхронизирующие последовательности. Обычно такая последовательность состоит из управляющего символа СОМ и трех специальных контрольных символов SKP.

На приемном конце, в зависимости от соотношения частот приемника и передатчика, данная последовательность передается в контроллер канального уровня без изменений, в нее вставляется дополнительный SKP символ или один из SKP символов убирается.

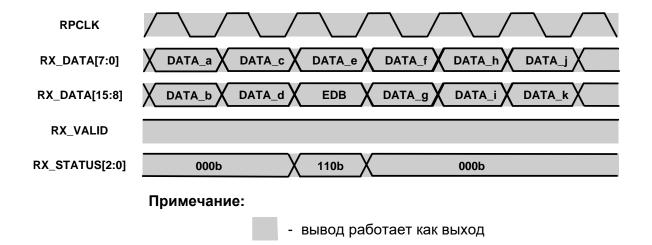

Выполняя такую вставку SKP символа или его удаление, СБИС 1888ВВ018А выдает на внешние выводы RX\_STATUS[2:0] код выполненной операции. Временные диаграммы обмена данными в этих случаях представлены на рисунках Рисунок 1.8Рисунок 1.9.

Рисунок 1.8 – Временная диаграмма передачи данных с вставкой SKP символа

|      |         |          |          |      |            |                 |              | Лист |  |

|------|---------|----------|----------|------|------------|-----------------|--------------|------|--|

|      |         |          |          |      |            | ЮФКВ.431268.019 | )PЭ          | 24   |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                 |              |      |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                 |              |      |  |

Рисунок 1.9 -Временная диаграмма передачи данных с удалением SKP символа

#### 1.5.5.5.3 Обнаружение ошибок во входном потоке данных

Интерфейс PIPE в СБИС 1888ВВ018А позволяет сообщать контроллеру канального уровня о возникновении различных ошибок во входном потоке данных. Возможно обнаружение следующих ошибок:

• Ошибка декодирования по алгоритму 8b/10b. Ошибка может возникнуть при обнаружении некорректных 8b/10b символов во входящем потоке данных. При возникновении этой ошибки на внешних выводах RX\_STATUS[2:0] устанавливается значение 100b и одновременно вместо ошибочного символа в контроллер канального уровня передается контрольный символ EDB. Временные диаграммы, поясняющие работу СБИС 1888ВВ018А при возникновении данной ошибки, приведены на Рисунок 1.10.

Рисунок 1.10 – Временная диаграмма передачи с ошибкой декодирования 8b/10b

|      |         |          |          |      |            |                 |              | Лист |

|------|---------|----------|----------|------|------------|-----------------|--------------|------|

|      |         |          |          |      |            | ЮФКВ.431268.019 | PЭ           | 25   |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                 |              | 25   |

| Инв  | .№подл. | Подп     | и дата   |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |

| 3′   | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                 |              |      |

• Ошибка диспаритета алгоритма 8b/10b. Ошибка может возникнуть при обнаружении несоответствия текущго и ожидаемого значения диспаритета принятых данных. Приемник не определяет, в каком из 2-х передаваемых по шине данных символов произошла ошибка диспаритета. Одновременно с символами, при приеме которых произошла данная ошибка, на внешние выводы RX\_STATUS[2:0] выставляется код ошибки 111b. Временные диаграммы, поясняющие работу СБИС 1888ВВ018А при возникновении данной ошибки, приведены на Рисунок 1.11.

Рисунок 1.11 – Временная диаграмма передачи с ошибкой диспаритета

• Ошибка опустошения адаптивного буфера. Ошибка может возникнуть при превышении тактовой частоты работы приемника над тактовой частотой работы передатчика и недостаточном количестве синхронизирующих последовательностей, вставленных в поток данных. При обнаружении этой ошибки приемник вставляет в поток данных контрольный символ EDB и выдает на внешние выводы RX\_STATUS[2:0] код ошибки 110b. Временные диаграммы, поясняющие работу СБИС 1888ВВ018А при возникновении данной ошибки, приведены на Рисунок 1.12.

|      |         |          |          |      |                   |            |              | Лист |  |

|------|---------|----------|----------|------|-------------------|------------|--------------|------|--|

|      |         |          |          |      | ЮФКВ.431268.019РЭ |            |              |      |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |                   |            |              |      |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№        | Инв.№дубл. | Подп. и дата |      |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3           |            |              |      |  |

Рисунок 1.12 – Временная диаграмма передачи с ошибкой опустошения адаптивного буфера

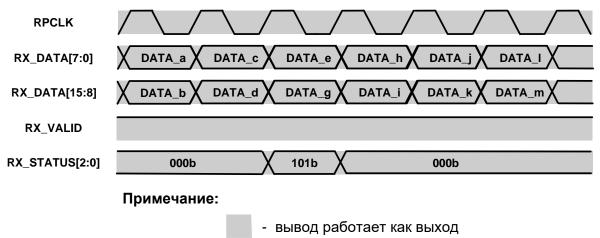

• Ошибка переполнения адаптивного буфера. Ошибка может возникнуть при превышении тактовой частоты работы передатчика над тактовой частотой работы приемника и недостаточном количестве синхронизирующих последовательностей, вставленных в поток данных. При обнаружении этой ошибки приемник на внешние выводы RX\_STATUS[2:0] выдается код ошибки 101b. Временные диаграммы, поясняющие работу СБИС 1888ВВ018А при возникновении данной ошибки, приведены на Рисунок 1.13.

Рисунок 1.13 – Временная диаграмма передачи с ошибкой переполнения адаптивного буфера

#### 1.5.5.5.4 Управление инверсией полярности линии

|      |         |          |          |      |            |                 |              | Лист |

|------|---------|----------|----------|------|------------|-----------------|--------------|------|

|      |         |          |          |      |            | ЮФКВ.431268.019 | )PЭ          | 27   |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                 |              | 21   |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.      | Подп. и дата |      |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                 |              |      |

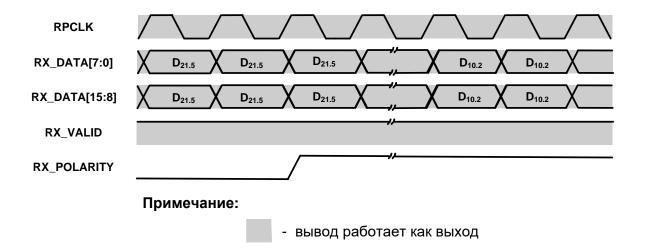

СБИС 1888ВВ018А поддерживает возможность инверсии полярности линии приемника. Это позволяет обеспечивать лучшую совместимость с различными реализациями устройств приемопередатчиков PCI Express. Инверсия полярности управляется входным сигналом RX\_POLARITY. Зависимость полярности принимаемых данных от состояния внешнего вывода RX\_POLARITY представлена в Таблица 1.9.

Таблица 1.9 - Зависимость полярности принимаемых данных от состояния внешнего вывода RX\_POLARITY.

| Внешний вывод | Функциональное              | Описание                               |

|---------------|-----------------------------|----------------------------------------|

|               | назначение                  |                                        |

| RX_POLARITY   | Управление полярностью      | 0 — Полярность данных не инвертируется |

|               | линии приемника PCI Express | 1 - Полярность данных инвертируется    |

Временные диаграммы, поясняющие работу СБИС 1888ВВ018А при изменении полярности линии, приведены на Рисунок 1.14.

Рисунок 1.14 — Временная диаграмма работы СБИС 1888 В В 018 А при изменении полярности линии

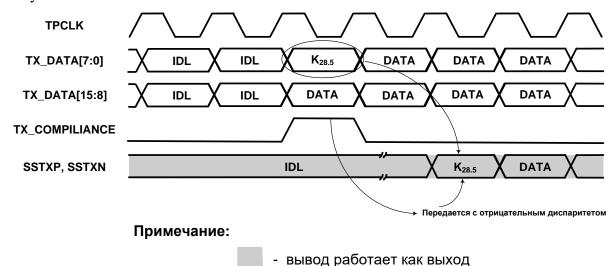

#### 1.5.5.5.5 Установка негативного значения диспаритета

Установка определенного значения диспаритета необходима для согласования диспаритета передатчика и приемника в начале передачи данных. При подаче высокого уровня на вход TX\_COMPLIANCE символ, передаваемый в данный момент по младшим разрядам шины TX\_DATA[15:0] кодируется передатчиком с определенным (отрицательным) значением диспаритета. Временные диаграммы, поясняющие работу

|      |         |          |          |      |            | ЮФКВ.431268.019РЭ |              |  |  |  |

|------|---------|----------|----------|------|------------|-------------------|--------------|--|--|--|

|      |         |          |          |      | 1          |                   |              |  |  |  |

| Изм. | Лист    | № докум. | Подп.    | Дата |            |                   |              |  |  |  |

| Инв  | .№подл. | Подп     | . и дата |      | Взам.инв.№ | Инв.№дубл.        | Подп. и дата |  |  |  |

| 3    | 1918-4  | Kah-     | 20.04.20 | 18   | 31918-3    |                   |              |  |  |  |

СБИС 1888ВВ018А при установке негативного значения диспаритета, приведены на Рисунок 1.15.

Рисунок 1.15 — Временная диаграмма работы СБИС 1888 ВВ018 А при установке отрицательного диспаритета

#### 1.5.5.5.6 Перевод передатчика в неактивное состояние

Состояние передатчика устанавливается установкой определенных значений на управляющем входе TX\_ELEC\_IDLE.

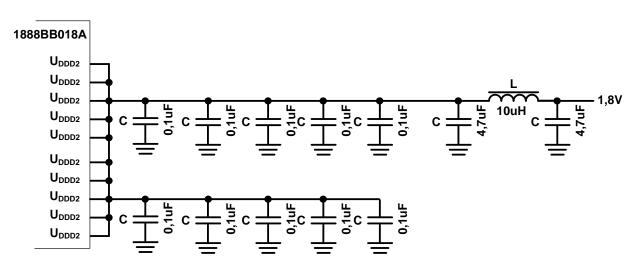

В режиме нормальной работы (состояние энергопотребления Р0) на данный вход должен быть подан сигнал низкого уровня. В этом случае передатчик работает в штатном режиме.